### **DESCRIPTION**

The PT2466 is a monolith integrated motor driver designed for gauge valves control, toy or power electronic locks. The overall performance is optimized for low supply voltage, battery-powered applications.

The superior low switches resistance (RDSon) minimized the power dissipates, therefore a small DFN and SOP-8 package is available for high current output, to prevent un-determinates miss operation, overall protections function was integrated such like over-current, under-voltage lockout and over temperature protection.

### APPLICATION

- Gauge valves

- Motor powered lenses

- Electronic locks

- Toys

- Robotics

#### **FEATURE**

- Single H-bridge driver could drive DC brushed Motor or solenoid loads.

- 1.8 Amps maximum DC output current

- Low power switches resistance:

0.28 Ω, high and low side both

- Dual supply power supply:

- For control logic (VCC): 1.8V ~ 6V

- For motor drives (VM): 0 to 12V

- Low power shutdown mode:

- Less than 10nA on all supply rail.

- Small Footprint Package

- 8-Pin DFN with Thermal PAD (2.0 X 2.0 mm)

- 8-Pin SOP

- Fully protection function includes VCC under voltage lockout (UVLO), over current protection and thermal shutdown.

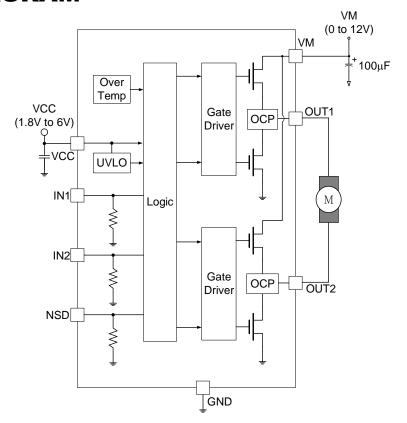

#### **BLOCK DIAGRAM**

Figure 1. Function Block Diagram

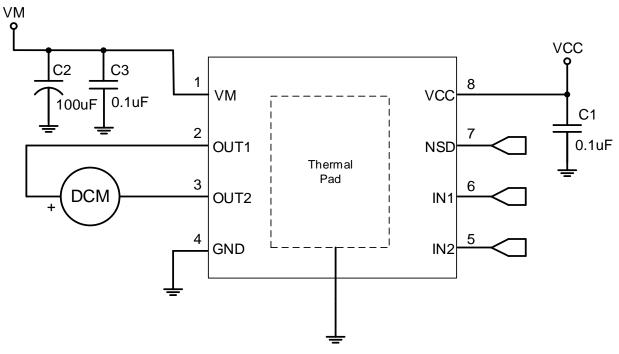

### **APPLICATION CIRCUIT**

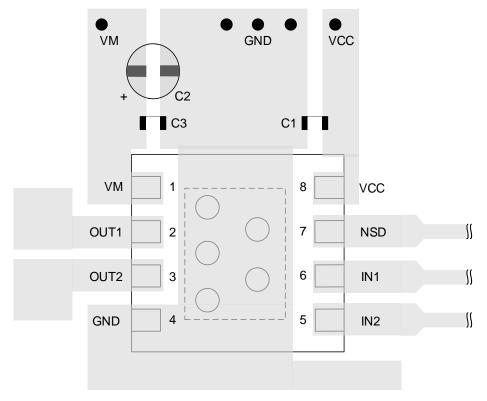

Figure 2. Schematic of Application

(Please refer to page 5 for bypass capacitor and PCB layout recommendation.)

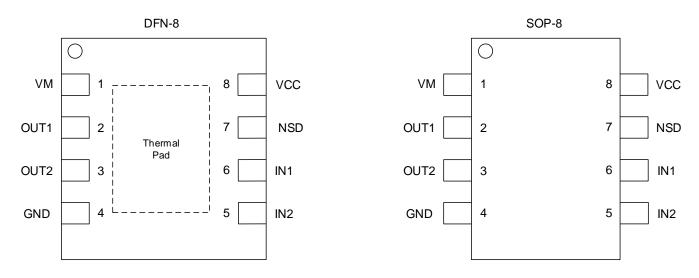

### **ORDER INFORMATION**

| Valid Part Number | Valid Part Number Package Type |          |

|-------------------|--------------------------------|----------|

| PT2466-S          | 8-Pin, SOP, 150 MIL            | PT2466-S |

| PT2466            | 8-Pins, DFN                    | 2466     |

### **PIN DESCRIPTION**

| Pin Name | I/O    | Description                    | Pin No. |

|----------|--------|--------------------------------|---------|

| VM       | POWER  | Power supply for motor drives  | 1       |

| OUT1     | OUTPUT | H-bridge output 1              | 2       |

| OUT2     | OUTPUT | H-bridge output 2              | 3       |

| GND      | POWER  | Ground                         | 4       |

| IN2      | INPUT  | Control logic input 2          | 5       |

| IN1      | INPUT  | Control logic input 1          | 6       |

| NSD      | INPUT  | Shutdown control input         | 7       |

| VCC      | POWER  | Power supply for control logic | 8       |

#### **FUNCTION DESCRIPTION**

#### H-BRIDGE OUTPUT DEFINITION

The output current of H-bridge driver is determinate by control logic interface; it also called a dual input interface (IN-

IN). Please refer to Table 1 for corresponds between input and output.

| NSD | IN1 | IN2 | OUT1 | OUT2 | DC Motor Operates |

|-----|-----|-----|------|------|-------------------|

| 0   | Х   | X   | HiZ  | HiZ  | Coast             |

| 1   | 0   | 0   | HiZ  | HiZ  | Coast             |

| 1   | 0   | 1   | L    | Н    | Reverse           |

| 1   | 1   | 0   | Н    | L    | Forward           |

| 1   | 1   | 1   | L    | L    | Brake             |

**Table 1. H-Bridge Output Definition**

#### FUNCTIONAL AND PROTECTION OPERATES

The PT2466 equipped fully protection function: please refer to the Table 2 for detail descriptions.

| Function Operation                                                                 | Criteria    | H-Bridge Outputs                                                                                                           |

|------------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------|

| VCC under veltage                                                                  | VCC < 1.7V  | All outputs disable                                                                                                        |

| VCC under-voltage                                                                  | VCC >1.8V   | Normal operates                                                                                                            |

|                                                                                    | IOUT < 1.8A | Normal operates                                                                                                            |

| Output over-current or short circuits, Includes shorted to VM, GND and cross load. | IOUT > 1.9A | All outputs disable for a short period (tRETRY) and release, this reaction will repeating until short circuits is removed. |

|                                                                                    | TJ < 160°C  | Normal operates                                                                                                            |

| Die temperature exceeds Thermal Shutdown limits                                    | TJ > 160℃   | All outputs disable and it will returns to normal operation until die temperature is lower than threshold.                 |

|                                                                                    | NSD = H     | Normal operates                                                                                                            |

| Power saving mode                                                                  | NSD = L     | All outputs disable and supply currents reduced to under 10nA.                                                             |

**Table 2. Functions Behavior**

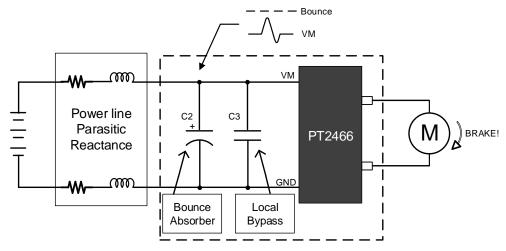

#### POWER SUPPLY CAPACITOR RECOMMENDATIONS

Consider a real world application scenario; the motor driver is designed to drives high inductance load such like motor winding or solenoid coil. If a H-bridge turns-off all of outputs during inductor current still flowing, because the inductor current would not be reset immediately, the rest of free-wheel current would re-directs and passing through the body diode of the output FET and runs into VM supply and final decay to zero after de-magnetization time. This reverse current depends on load inductance, inductor current and re-generates current from the motor due to inertia of rotor.

In another case, the parasitic reactance (inductance + resistance) of power wire between the power supply and motor driver board with parasitic capacitance of PCB consists a LC resonates tank, during power supply sourcing current to the motor driver board, the VM voltage may drops quickly and parasitic LC will be trigged and shows oscillation spike if the local bypass capacitor is not sufficient.

To prevent unstable bounce or spike appears on VM bus, a high capacitance bounce absorber capacitor (>100 $\mu$ F) should be placed on VM bus line, it could absorb re-generates free-wheels current during DC motor brake and stabilize VM voltage during high forward/reverse motor current sources. A small MLCC 0.1 $\mu$ F bypass capacitor should be placed near the motor driver IC power pin, VM and VCC both, to reduce the spike causes by power line LC resonates.

Figure 3. Motor Driver System with External Power Supply

#### PCB LAYOUT RECOMMENATION

The local bypass capacitor C1 and C3 should be placed near the IC power pins, and bounce absorber capacitor C2 should be placed on VM bus line. The GND plane should be placed on the component side under the chip as a low impedance power trace, and larger area of GND plane and wider cooper trace reduce the thermal resistance( $\theta_{JA}$ ). The thermal pad under DFN package should be soldered to the PCB component side and connects to the bottom side through the via holes, this arrangement can further enhance the heat dissipation.

Figure 4. Simplified Layout Example

### **ABSOLUTE MAXIMUM RATINGS**

| Parameters   |                        |      | Min  | Max | Unit |

|--------------|------------------------|------|------|-----|------|

| Motor power  | er supply voltage , VM |      | -0.3 | 13  | V    |

| Logic powe   | er supply voltage, VCC | ;    | -0.3 | 6.5 | V    |

| Operating 7  | Temperature, Top       |      | -40  | 150 | °C   |

| Storage Te   | emperature, Tstg       |      | -40  | 150 | °C   |

| Operation I  | Humidity               |      | 20   | 85  | %    |

| Storage Hu   | umidity                |      | 20   | 90  | %    |

| НВМ          |                        | ±4   |      | KV  |      |

| ESD All Pins |                        | MM   | ±0.4 |     | KV   |

|              |                        | CDM* | ±1.5 |     | KV   |

<sup>\*</sup>CDM test is based on ANSI/ESDA/JECEC JS-002-2014

### RECOMMENDED OPERATING CONDITIONS

|              | Parameters                       | Min | Max | Unit |

|--------------|----------------------------------|-----|-----|------|

| VM           | Motor power supply voltage       | 0   | 12  | V    |

| VCC          | Logic power supply voltage       | 1.8 | 6   | V    |

| Іоит         | Motor peak current               | 0   | 1.8 | А    |

| <b>f</b> PWM | Externally applied PWM frequency | 0   | 250 | KHz  |

| VLOGIC       | Logic level input voltage        | 0   | 6   | V    |

| TA           | Operating ambient temperature    | -40 | 85  | °C   |

### **PACKAGE THERMAL CHARACTERISTICS**

PACKAGE: DFN

| Parameter                                                 | Symbol | Value | Unit |

|-----------------------------------------------------------|--------|-------|------|

| From chip conjunction dissipation to external environment | θЈА    | 75.6  | °C/W |

PACKAGE: SOP, 150MIL

| Parameter                                                 | Symbol | Value | Unit |

|-----------------------------------------------------------|--------|-------|------|

| From chip conjunction dissipation to external environment | θЈА    | 113.9 | °C/W |

### **ELECTRICAL CHARACTERISTICS**

| Symbol           | Parameter                          | Test Conditions                              | Min      | Тур      | Max     | Unit |

|------------------|------------------------------------|----------------------------------------------|----------|----------|---------|------|

| -                | pplies(VM, VCC)                    |                                              |          | 71       |         |      |

| VM Currer        |                                    |                                              |          |          |         |      |

| I <sub>VM1</sub> | VM coast current                   | VM=5V; VCC=3V; No PWM<br>Coast Mode          |          | 65       | 90      | μA   |

| I <sub>VM2</sub> | VM F/R current                     | VM=5V; VCC=3V; No PWM Forward/Reverse Mode   |          | 300      | 500     | μA   |

| Ivмз             | VM brake current                   | VM=5V; VCC=3V; No PWM Brake Mode             |          | 65       | 90      | μA   |

| <b>I</b> ∨M4     | VM PWM current                     | VM=5V ; VCC=3V<br>PWM=50KHz                  |          | 240      | 400     | μΑ   |

| IVMQ             | VM sleep current                   | VM=5V; VCC=3V NSD=L                          |          | 5        |         | nA   |

| VCC Curre        | ent                                |                                              |          |          | -       |      |

| Ivcc1            | VCC coast current                  | VM=5V ; VCC=3V ; No PWM<br>Coast Mode        |          | 380      | 500     | μΑ   |

| Ivcc2            | VCC F/R current                    | VM=5V ; VCC=3V ; No PWM Forward/Reverse Mode |          | 450      | 650     | μΑ   |

| Ічссз            | VCC brake current                  | VM=5V ; VCC=3V ; No PWM<br>Brake Mode        |          | 480      | 650     | μΑ   |

| Ivcc4            | VCC PWM current                    | VM=5V ; VCC=3V<br>PWM=50KHz                  |          | 450      | 650     | μΑ   |

| Ivccq            | VCC shutdown current               | VM=5V; VCC=3V, NSD=L                         |          | 2        |         | nA   |

| Control L        | ogic Inputs (IN1, IN2, NSD)        |                                              |          |          |         |      |

| VIL              | Input logic low voltage            |                                              |          |          | 0.3*VCC | V    |

| VIH              | Input logic high voltage           |                                              | 0.5*VCC  |          |         | V    |

| lıL              | Input logic low current            | V <sub>IN</sub> =0V                          |          |          | 5       | μA   |

| Іін              | Input logic high current           | V <sub>IN</sub> =3.3V                        |          |          | 50      | μA   |

| Rpd              | Pulldown resistance                | IN1, IN2, NSD                                |          | 100      |         | ΚΩ   |

| H-Bridge         | Driver Outputs (OUT1, OUT2)        |                                              |          |          |         |      |

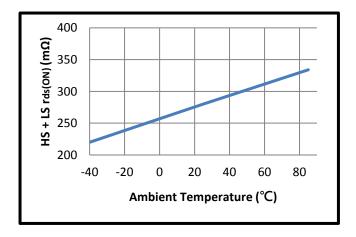

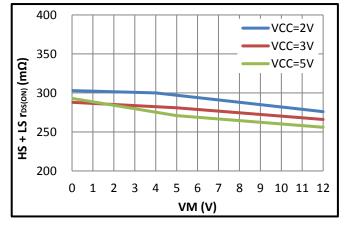

| RDS(ON)          | HS + LS switch ON resistance       | VM=5V; VCC=3V;<br>Io=800mA; Tj=25°C          |          | 280      |         | mΩ   |

| loff             | Off-state leakage current          | Output=OPEN                                  |          | 5        |         | nA   |

| Protection       | •                                  | Output-Of LIV                                | <u> </u> | <u> </u> |         | шл   |

| i rotcotioi      |                                    | VCC falling                                  |          |          | 1.7     | V    |

| $V_{\sf UVLO}$   | VCC under-voltage lockout          | VCC rising                                   | 1.8      |          | 1.7     | V    |

| Іоср             | Over-current protection trip level |                                              | 1.9      |          | 3.5     | A    |

| tretry           | Over-current retry time            |                                              |          | 1        |         | mS   |

| Тотр             | Thermal shutdown temperature       | Die temperature                              |          | 160      |         | °C   |

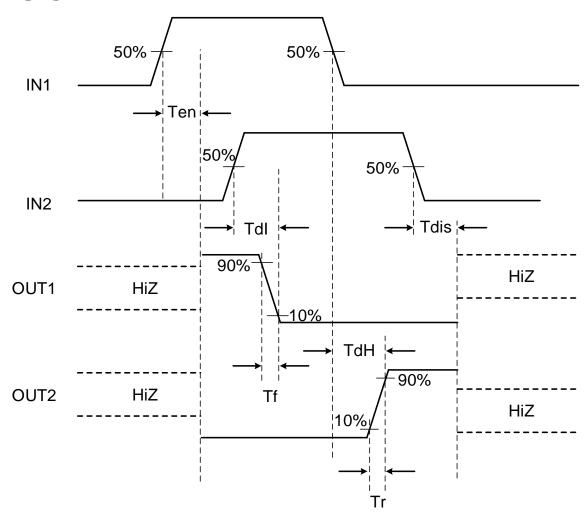

| I/O Propa        | gation Delay and Timing Require    | ment                                         | <u> </u> |          | 1       | I    |

| Ten              | Output enable time                 |                                              |          |          | 0.8     | μS   |

| Tdis             | Output disable time                | TA=25°C, VM=5V, VCC=3V,                      |          |          | 0.8     | μS   |

| Tdh              | Delay time, INx high to OUTx high  | RL=47Ω                                       |          |          | 0.7     | μS   |

| Tdl              | Delay time, INx low to OUTx low    | ]                                            |          |          | 0.7     | μS   |

| Symbol | Parameter                                    | Test Conditions | Min | Тур | Max | Unit |

|--------|----------------------------------------------|-----------------|-----|-----|-----|------|

| Tr     | Output rise time                             |                 |     |     | 0.5 | μS   |

| Tf     | Output fall time                             |                 |     |     | 0.5 | μS   |

| i isan | Wake time , NSD rising edge to output active |                 |     |     | 5   | μS   |

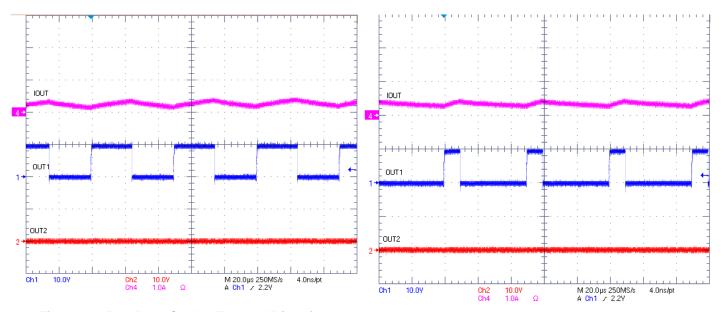

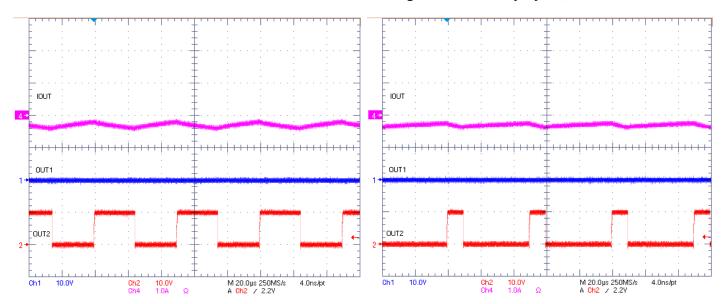

## **TIMING CHART**

**Figure 5. Input and Output Timing**

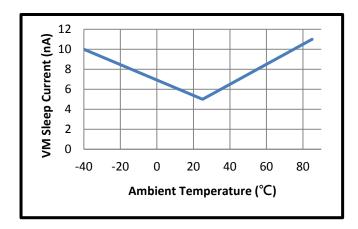

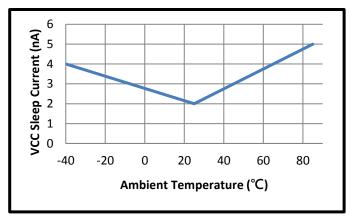

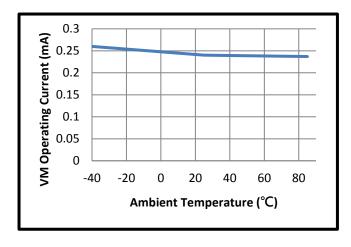

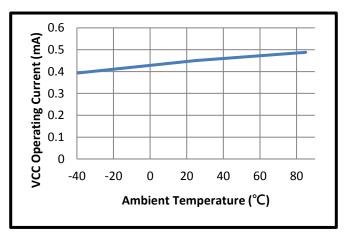

### TYPICAL OPERATING CHARACTERISTICS

(VM=5V, VCC=3V unless otherwise noted)

Figure 6. IVMQ vs TA

Figure 7. IVCCQ vs TA

Figure 8. IVM vs TA (50KHz PWM)

Figure 9. IVCC vs TA (50KHz PWM)

Figure 10. HS + LS rps-on vs TA

Figure 11. HS + LS rps-on vs VM

Figure 12. 50% Duty Cycle , Forward Direction

Figure 13. 20% Duty Cycle , Forward Direction

Figure 14. 50% Duty Cycle , Reverse Direction

Figure 15. 20% Duty Cycle, Reverse Direction

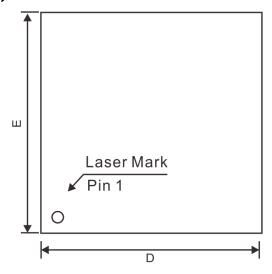

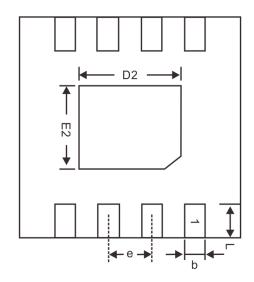

# **PACKAGE INFORMATION**

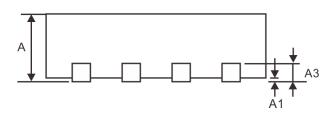

# 8-PIN, DFN

| Cumb al |          | Dimensions(mm) |      |  |

|---------|----------|----------------|------|--|

| Symbol  | Min.     | Nom.           | Max. |  |

| Α       | 0.70     | 0.75           | 0.80 |  |

| A1      | 0.00     | 0.02           | 0.05 |  |

| A3      | 0.20 REF |                |      |  |

| b       | 0.18     | 0.25           | 0.30 |  |

| D       |          | 2.00 BSC       |      |  |

| Е       |          | 2.00 BSC       |      |  |

| е       |          | 0.50 BSC       |      |  |

| D2      | 1.50     | 1.60           | 1.65 |  |

| E2      | 0.80     | 0.90           | 0.95 |  |

| L       | 0.25     | 0.30           | 0.35 |  |

Note: Refer to JEDEC MO-229

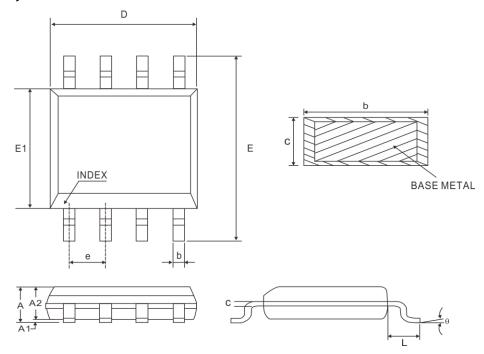

# 8 PINS, SOP, 150MIL

| Cumbal |      | Dimensions(mm) |      |  |  |  |

|--------|------|----------------|------|--|--|--|

| Symbol | Min. | Nom.           | Max. |  |  |  |

| A      | -    | -              | 1.75 |  |  |  |

| A1     | 0.10 | -              | 0.25 |  |  |  |

| A2     | 1.25 | -              | -    |  |  |  |

| b      | 0.31 | -              | 0.51 |  |  |  |

| С      | 0.10 | -              | 0.25 |  |  |  |

| D      |      | 4.90 BSC       |      |  |  |  |

| Е      |      | 6.00 BSC       |      |  |  |  |

| E1     |      | 3.90 BSC       |      |  |  |  |

| е      |      | 1.27BSC        |      |  |  |  |

| L      | 0.40 | -              | 1.27 |  |  |  |

| θ      | 0°   | -              | 8°   |  |  |  |

Notes: Refer to JEDEC MS-012 AA

#### **IMPORTANT NOTICE**

Princeton Technology Corporation (PTC) reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and to discontinue any product without notice at any time. PTC cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a PTC product. No circuit patent licenses are implied.

Princeton Technology Corp. 2F, 233-1, Baociao Road, Sindian Dist., New Taipei City 23145, Taiwan

Tel: 886-2-66296288 Fax: 886-2-29174598 http://www.princeton.com.tw